| МђНщ

ЁЁЁЁIEEE 1588БъзМЕЎЩњгк2002ФъЃЌжївЊЖЈвхЭјТчЗжВМЪНЪБжгЕФЭЌВНавщЁЃВтЪдгыВтСПЁЂЕчаХКЭЖрУНЬхСїДІРэЕШаэЖрВЛЭЌгІгУЃЌЖМПЊЪМЪзбЁетжжЪБжгЭЌВНЗНЗЈЁЃетжжБъзМЛЏЪБжгЭЌВНЗЈГЩБОаЇвцИпЃЌжЇГжвьЙЙЯЕЭГЃЌВЂПЩЬсЙЉФЩУыМЖЭЌВНОЋЖШЁЃ

ЁЁЁЁБОЮФНщЩмдАцIEEE 1588-2002БъзМвдМАИќаТАцБОIEEE 1588-2008жаЕФИФНјФкШнЁЃгЩгкIEEE 1588дквЛаЉФПБъгІгУжадНРДдНживЊЃЌвђДЫADSP-BF5181Blackfin®ЧЖШыЪНДІРэЦїжавВМЏГЩзЈгУгВМўРДжЇГжIEEE 1588ЁЃБОЮФНЋИХвЊНщЩмЦфЙІФмЃЌВЂЭЈЙ§вЛИіЪОР§РДеЙЪОРћгУADSP-BF518ДІРэЦїНтОіЗНАИЛёЕУЕФЪБжгЭЌВНадФмНсЙћЁЃ

ЁЁЁЁЯждкМИЕуСЫЃП

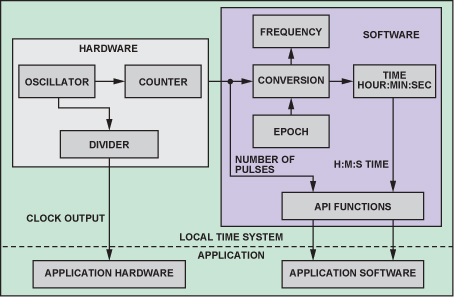

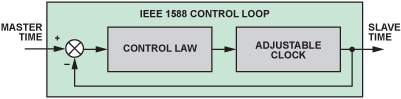

ЁЁЁЁДѓЖрЪ§ЯЕЭГЖМашвЊРћгУБОеёРДЮЌЛЄздМКЕФЪБМфИХФюЁЃЭМ1ЯдЪОгВМўКЭШэМўШчКЮзщКЯЃЌдкЯЕЭГФкВњЩњЪБМфаХЯЂЁЃ

ЁЁЁЁ

ЁЁЁЁЭМ1. БОЕиМЦЪБ

ЁЁЁЁЯЕЭГФкЕФгВМўКЭШэМўзЪдДОљПЩЪЙгУДЫЪБМфаХЯЂЁЃЖдгкгВМўЃЌеёЕДЦїЪБжгЛсВњЩњвЛИіЛђЖрИіЮяРэЪБжгаХКХЃЈЪБжгЪфГіЃЉЃЌВЂПЩРћгУетаЉЪБжгаХКХЧ§ЖЏЛђДЅЗЂЯЕЭГЕФЦфЫќВПЗжЁЃШэМўжаЮЌЛЄЕФЪБМфЭЈГЃГЦЮЊЁАЯЕЭГЪБМфЁБЁЃЯЕЭГЪБМфПЩвдгУЪБжгТіГхЪ§ЛђУы/ФЩУыЕФаЮЪНБэЪОЁЃЯЕЭГШэМўРћгУеёЕДЦїЪБжгТіГхЪ§МАЦфЦЕТЪаХЯЂЕУГіЪБМфЃЌВЂЬсЙЉЁАгІгУГЬађБрГЬНгПкЁБ(API)КЏЪ§ЃЌШэМўЕФЦфЫќВПЗжПЩвдЪЙгУетаЉКЏЪ§МьЫїВЂЩшжУЪБМфЁЃШчЙћашвЊОјЖдЪБМфЃЌдђЫљЬсЙЉЕФЪБМфНЋгыдЄЖЈвхЪБМфЕуЃЌМДЛљзМЪБМфЕуЯрЙиСЊЁЃ

ЁЁЁЁЪБжгЭЌВН

ЁЁЁЁаэЖргІгУвЊЧѓСНЬЈЖРСЂЕФЩшБИвдЭЌВНЗНЪНЙЄзїЁЃШчЙћУПЬЈЩшБИНівРППздМКЕФеёЕДЦїЃЌдђИїеёЕДЦїЕФЬиадгыЙЄзїЬѕМўВювьНЋЛсЯожЦЪБжгЭЌВНЙЄзїЕФФмСІЁЃвЛаЉМђЕЅПЩааЕФНтОіЗНАИПЩвдПЫЗўетаЉЯожЦЃЌАќРЈЃК

ЁЁЁЁЫљгаЩшБИЙВгУвЛИіЮяРэеёЕДЦїЁЃетжжЗНЗЈНіЖдОрРыКмНќЕФЗжВМЪНЯЕЭГПЩааЃЛИпЦЕЪБжгаХКХЮоЗЈЪЕЯжГЄОрРыПЩППДЋЪфЁЃ

ЫљгаЩшБИОљЪЙгУЬиадМИКѕЭъШЋЯрЭЌЕФеёЕДЦїЁЃгЩгкКмФбЛёЕУМИКѕЭъШЋвЛбљЕФеёЕДЦїЃЌВЂШЗБЃадФмВЛЫцЪБМфЦЎвЦЃЌвђДЫетжжЗНЗЈВЛПЩааЁЃИќживЊЕФЪЧЃЌИїеёЕДЦїЕФЙЄзїЬѕМўВЂВЛЯрЭЌЁЃ

ШчЙћЫљгаЩшБИОљЭЈЙ§вЛИіЭЈаХЭјТчЃЈР§ШчвдЬЋЭјЃЉЛЅСЌЃЌдђетаЉЩшБИПЩвдЭЈЙ§ЭјТчНЛЛЛЪБМфЯћЯЂЃЌИљОнЕЅИіЁАжїЁБЪБжгЖЏЬЌЕїећИїздЕФЪБжгЁЃРћгУДЋЭГЕФЪБМфЭЌВНавщЁЊЁЊЁАЭјТчЪБМфавщЁБ(NTP)ЃЌЯЕЭГжаЕФУПЬЈЩшБИИљОнЫќДгNTPЪБМфЗўЮёЦїЛёШЁЕФЪБМфаХЯЂЕїећЦфЪБжгЁЃШЛЖјЃЌИУавщжЛФмЪЕЯжКСУыМЖЭЌВНОЋЖШЁЃ

IEEE 1588ЖЈвхСЫвЛИіаТавщЃЌФмЙЛЪЕЯжФЩУыМЖЭЌВНОЋЖШЁЃЯТУцЬжТлИУБъзМШчКЮЪЕЯжетжжЫЎЦНЕФЪБжгЭЌВНЁЃ

ЁЁЁЁIEEE 1588гаКЮзїгУ

ЁЁЁЁIEEE 1588БъзМЖЈвхСЫвЛжжЪБМфЭЌВНавщЃЌЪЪгУгкЕиРэЮЛжУЗжЩЂЕЋЭЈЙ§ФГжжЭЈаХММЪѕЃЈР§ШчвдЬЋЭјЃЉЛЅСЌЕФЩшБИЁЃЩшБИжЎМфЭЈЙ§НЛЛЛЪБађЯћЯЂЃЌДгЖјБЃГжЯрЭЌЕФОјЖдЯЕЭГЪБМфЃЈгУУыКЭФЩУыБэЪОЃЉЁЃ

ЁЁЁЁвЊЪЕЯжДЫФПБъЃЌвЛИіжБЙлЕФЗНЗЈЪЧНЋвЛЬЈОпгаЁАзюМбЁБЃЈзюОЋШЗЃЉЪБжгЕФЩшБИжИЖЈЮЊЁАжїЪБжгЁБЩшБИЃЌШУЫќЯђЦфЫќЩшБИЙуВЅЦфЪБМфЁЃЦфЫќЩшБИНЋЛсЕїећИїздЕФЪБМфЃЌгыжїЪБжгЫљЗЂЫЭЕФЪБМфБЃГжвЛжТЁЃВЛЙ§ЃЌетжжНтОіЗНАИвВгаМИЕуВЛзуЃК

ЁЁЁЁжїЪБжгЩшБИЮоЗЈвдМЋЖЬЕФМфИєЙуВЅЪБМфЃЌвђДЫЁАДгЁБЪБжгЩшБИБиаыЪЙгУздМКЖРСЂЕФЁАЕЭСгЁБеёЕДЦїЃЌдкжїЪБжгЩшБИЕФСНДЮЙуВЅжЎМфВхШыЪБМфЕуЁЃетНЋЕМжТжїЪБжгИќаТжмЦкжЎМфЕФЭЌВНОЋЖШЯТНЕЁЃ

ЙуВЅТЗОЖФбУтДцдкбгГйЃЌбгГйЗљЖШШЁОігкЭЈаХММЪѕЃЌР§ШчЮяРэаХКХбиЕМЯпДгвЛЬЈЩшБИДЋЪфжССэвЛЬЈЩшБИЫљашЕФЪБМфЁЃетжжбгГйЛсНјвЛВНРЉДѓжїЪБжггыИїДгЪБжгжЎМфЕФЪЇЕїЁЃ

жїЪБжгЩшБИгыИїДгЪБжгЩшБИжЎМфЕФЙуВЅТЗОЖДцдкВювьЃЌетЛсНјвЛВННЕЕЭИїДгЪБжгЩшБИжЎМфЕФЭЌВНОЋЖШЁЃ

IEEE 1588вЊЧѓЭЈЙ§ВтСПТЗОЖбгГйЃЌНтОіЕкЖўИіКЭЕкШ§ИіЮЪЬтЁЃЫќЛЙвЊЧѓД§ЕїећЕФДгЪБжггыжїЪБжгБЃГжВНЕївЛжТЃЌДгЖјМѕЧсЕквЛИіЮЪЬтЁЃШчЙћПЩФмЃЌЪЙгУИќаЁЕФЙуВЅМфИєКЭИќИпжЪСПЕФеёЕДЦїЃЌПЩвдНјвЛВНМѕЧсЕквЛИіЮЪЬтЁЃ

ЁЁЁЁIEEE 1588ШчКЮВтСПЭЈаХбгГй

ЁЁЁЁIEEE 1588-20022 ЖЈвхСЫЫФжжЯћЯЂSyncЁЂFollowupЁЂDelayReqКЭDelayRespЃЌгУРДВтСПЧАЯђЃЈжїЪБжгжСДгЪБжгЃЉКЭКѓЯђЃЈДгЪБжгжСжїЪБжгЃЉТЗОЖЕФЭЈаХбгГйЁЃИќаТАцБОIEEE 1588-2008,3ЛЙЬсЙЉЦфЫќЛњжЦЃЌаТдіШ§жжЯћЯЂЃКPdelayReqЁЂPdelayRespКЭ PdelayRespFollowupРДВтСПЁАЕуЖдЕубгГйЁБЁЃ

ЁЁЁЁетаЉЯћЯЂжаЃЌSyncЁЂDelayReqЁЂPdelayReqКЭPdelayRespЪЧЫљЮНЁАЪТМўЁБЯћЯЂЃЌдкРыПЊКЭЕНДявЛЬЈЩшБИЪББиаыМгЩЯЁАЪБМфДСЁБЃЈМЧТМБОЕиЪБМфЃЉЁЃИјЗжзщМгЩЯЪБМфДСЕФЗНЗЈгаСНжжЃК

ЁЁЁЁ1.ЁЁЯћЯЂгЩШэМўДІРэЪБГіЯжШэМўЪБМфДСЁЃЭЈГЃГіЯждкЯћЯЂЕФНгЪе/ЗЂЫЭЁАжаЖЯЗўЮёГЬађЁБ(ISR)жаЃЌИУЪБМфДСЮЊЯЕЭГЪБМфЕФЕБЧАжЕЁЃ

ЁЁЁЁ2.ЁЁЯћЯЂЪЕМЪЕНДяЛђРыПЊЩшБИЪБГіЯжгВМўЪБМфДСЁЃИУЪБМфДСВйзїгЩгВМўжДааЃЌгВМўЛсЮЌЛЄздМКЕФСЌајЪБМфаХЯЂЁЃ

ЁЁЁЁСНжжЪБМфДСЗНЗЈОљЮЊIEEE 1588ЫљНгЪмЃЌЕЋгВМўЪБМфДСЕФОЋЖШУїЯдИќИпЃЌШчЯТЮФЫљЪіЁЃ

ЁЁЁЁжїЪБжгЩшБИЕНДгЪБжгЩшБИЕФбгГй

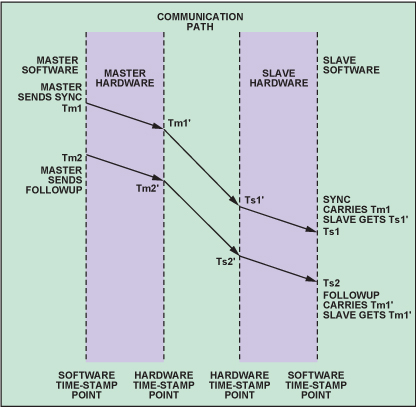

ЁЁЁЁЯћЯЂSyncКЭFollowupгЩжїЪБжгЩшБИЗЂЫЭЃЌДгЪБжгЩшБИИКд№НгЪеетаЉЯћЯЂЃЌВЂМЦЫужїЪБжгЩшБИЕНДгЪБжгЩшБИЕФЭЈаХТЗОЖбгГйЁЃ

ЁЁЁЁЭМ2жаЃЌдкЪБМфЕуTm1ЃЌжїЪБжгЩшБИШэМўЖСШЁЕБЧАБОЕиЯЕЭГЪБМфЃЈTm1ЃЌШэМўЪБМфДСЃЉЃЌНЋЦфВхШыSyncЯћЯЂжаЃЌВЂЫЭГіИУЯћЯЂЁЃИУЯћЯЂдкЩдКѓЕФЪБМфЕуTm1'РыПЊжїЪБжгЩшБИЃЌИУЪБМфЕуЮЊгВМўЪБМфДСЁЃИУЯћЯЂдкЪБМфЕуTs1'ЃЈДгЪБжгЩшБИБОЕиЪБМфЃЉЕНДяДгЪБжггВМўЃЌДгЪБжгЩшБИШэМўдкЩдКѓЕФЪБМфЕуTs1ЪеЕНИУЯћЯЂЁЃИУШэМўНЋЖСШЁгВМўЪБМфДСвдЛёЕУTs1'ЁЃШчЙћУЛгаЭЈаХбгГйЃЌTs1'гІЕШгк(Tm1' + Tms)ЃЌЦфжаTmsЮЊжїЪБжггыДгЪБжгжЎМфЕФЪБМфВюЁЃИУавщЕФзюжеФПБъЪЧВЙГЅДЫЪБМфВюЁЃ

ЁЁЁЁ

ЁЁЁЁЭМ2. ВтСПжїЪБжгЩшБИгыДгЪБжгЩшБИжЎМфЕФЭЈаХбгГй

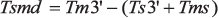

ЁЁЁЁЗЂЫЭSyncЯћЯЂжЎКѓЃЌжїЪБжгЩшБИШэМўЭЈЙ§ЪБМфДСЕЅдЊЖСШЁSyncЯћЯЂЕФРыПЊЪБМфTm1'ЃЌНЋЦфВхШыFollowupЯћЯЂжаЃЌШЛКѓдкЪБМфЕуTm2ЗЂЫЭИУЯћЯЂЁЃДгЪБжгЩшБИШэМўдкЪБМфЕуTs2ЪеЕНДЫЯћЯЂЁЃДЫЪБЃЌДгЪБжгЩшБИШэМўгаСНИіЪБМфЃКTs1'ЃЈSyncЕНДяЪБМфЃЉКЭTm1'ЃЈSyncРыПЊЪБМфЃЉЁЃжїДгТЗОЖбгГйTmsdгЩЙЋЪН1ШЗЖЈЁЃ

ЁЁЁЁ (1) (1)

ЁЁЁЁДгЪБжгЩшБИЕНжїЪБжгЩшБИЕФбгГй

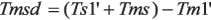

ЁЁЁЁДгЪБжгЩшБИЗЂЫЭDelayReqЯћЯЂЃЌжїЪБжгЩшБИгшвдЯьгІЗЂЫЭDelayRespЯћЯЂЁЃРћгУетаЉЯћЯЂЃЌДгЪБжгЩшБИПЩвдМЦЫуДгЪБжгЩшБИЕНжїЪБжгЩшБИЕФЭЈаХТЗОЖбгГйЁЃ

ЁЁЁЁдкЪБМфЕуTs3ЃЈЭМ3ЃЉЃЌДгЪБжгЩшБИШэМўЖСШЁЕБЧАБОЕиЯЕЭГЪБМфЃЈTs3ЃЉЃЌНЋЦфВхШыDelayReqЯћЯЂжаЃЌВЂЫЭГіИУЯћЯЂЁЃ

ЁЁЁЁ

ЁЁЁЁЭМ3. ВтСПДгжїЭЈаХбгГй

DelayReqЯћЯЂдкЩдКѓЕФЪБМфЕуTm3'ЕНДяжїЪБжгЩшБИЃЌгЩжїЪБжгЩшБИШэМўдкЪБМфЕуTm3ДІРэЁЃШЛКѓЃЌИУШэМўЖСШЁЪБМфДСвдЛёШЁЕНДяЪБМфTm3'ЃЌНЋЦфВхШыDelayRespЯћЯЂжаЃЌВЂдкЪБМфЕуTm4ЗЂЫЭжСДгЪБжгЩшБИЁЃЕБДгЪБжгЩшБИШэМўдкЪБМфЕуTs4ЪеЕНDelayRespЯћЯЂЪБЃЌЫќПЩвдЬсШЁЪБМфTm3'ЃЌВЂЭЈЙ§ЙЋЪН2МЦЫуДгжїЭЈаХбгГйTsmdЁЃ

ЁЁЁЁ  ; (2) ; (2)

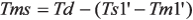

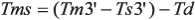

ЁЁЁЁЙЋЪН1КЭЙЋЪН2жаОљгавЛИіЮДжЊБфСПЃЌМДжїДгЪБМфВюTmsЃЌвђДЫЮоЗЈЕЅЖРЧѓЕУTmsdЛђTsmdЁЃЕЋЪЧЃЌШчЙћЮвУЧКЯРэЕиМйЩшЭЈаХТЗОЖЪЧЖдГЦЕФЃЌМД

ЁЁЁЁ  (3) (3)

ЁЁЁЁЁЊЁЊетЪЧIEEE 1588ГЩСЂЕФЙиМќМйЩшЁЊЁЊФЧУДЃЌНЋЙЋЪН1гыЙЋЪН2ЯрМгПЩвдЕУГіЃК

ЁЁЁЁ  (4) (4)

ЁЁЁЁгЩгкДгЪБжгЩшБИбАЧѓгыжїЪБжгЩшБИЭЌВНЃЌвђДЫЫљгаетаЉМЦЫуОљгЩетаЉЩшБИжДааЁЃДгЪБжгЩшБИДгжїЪБжгЩшБИЕФFollowupЯћЯЂЛёЕУTm1'ЃЌДгЦфRxЃЈНгЪеЃЉЪБМфДСЛёЕУTs1'ЃЌДгЦфTxЃЈЗЂЫЭЃЉЪБМфДСЛёЕУTs3'ЃЌВЂЭЈЙ§жїЪБжгЩшБИЕФDelayRespЯћЯЂЛёЕУTm3'ЁЃ

ЁЁШчКЮМЦЫуДгЪБжггыжїЪБжгЕФЪБМфВю

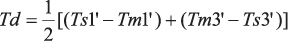

ЁЁЁЁвЛЕЉЛёЕУЭЈаХТЗОЖбгГйTdЃЌБуПЩРћгУЙЋЪН1ЛђЙЋЪН2ЧсЫЩМЦЫуДгЪБжггыжїЪБжгЕФЪБМфВюЃЌШчЙЋЪН5КЭЙЋЪН6ЫљЪОЁЃ

ЁЁЁЁ (5) (5)

(6) (6)

ЁЁЁЁШчКЮЕїећДгЪБжгЩшБИЕФЪБМф

ЁЁЁЁжЊЕРгыжїЪБжгЕФЪБМфВюжЎКѓЃЌИїДгЪБжгашвЊЕїећздМКЕФБОЕиЪБМфЃЌгыжїЪБжгБЃГжвЛжТЁЃИУШЮЮёАќРЈСНЗНУцЁЃЕквЛЃЌДгЪБжгЩшБИашвЊМгЩЯЪБМфВювдЕїећОјЖдЪБМфЃЌЪЙЦфЪБМфдкДЫПЬгыжїЪБжгЪБМфЭъШЋвЛжТЁЃЕкЖўЃЌДгЪБжгЩшБИашвЊЕїећИїздЕФЪБжгЦЕТЪЃЌгыжїЪБжгЕФЦЕТЪБЃГжвЛжТЁЃЮвУЧВЛФмЕЅППОјЖдЪБМфЃЌвђЮЊЪБМфВюНідквЛЖЈЦкМфФкгІгУЃЌПЩФмЪЧе§жЕЃЌвВПЩФмЪЧИКжЕЃЛЕїећЕФНсЙћЪЧДгЪБжгЪБМфЯђЧАЬјдОЛђЯђКѓЕЙЭЫЁЃвђДЫЃЌдкЪЕМЪВйзїжаЃЌЕїећЗжСНВНжДааЃК

ЁЁЁЁ1. ШчЙћЪБМфВюЙ§ДѓЃЌР§Шч1УывдЩЯЃЌдђгІгУОјЖдЪБМфЕїећЁЃ

ЁЁЁЁ2. ШчЙћЪБМфВюНЯаЁЃЌдђЪЙДгЪБжгЕФЦЕТЪИФБфФГвЛАйЗжБШЁЃ

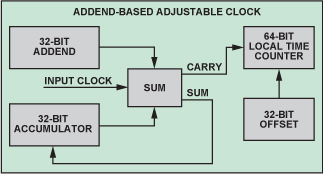

ЁЁЁЁвЛАуЖјбдЃЌИУЯЕЭГЛсБфГЩвЛИіПижЦЛЗТЗЃЌЦфжажїЪБжгЪБМфЪЧВЮПМУќСюЃЌЖјДгЪБжгЪБМфЪЧИњзйжїЪБжгЪБМфЕФЪфГіЃЌЖўепжЎВюЧ§ЖЏПЩЕїећЪБжгЁЃПЩвдЪЙгУPIDПижЦРДЪЕЯжЬиЖЈИњзйадФмЃЌетЪЧаэЖрIEEE 1588ЪЕЪЉЗНАИГЃгУЕФЗНЗЈЁЃЭМ4ЯдЪОСЫетжжПижЦЛЗТЗЁЃ

ЁЁЁЁ

ЁЁЁЁЭМ4. IEEE 1588ПижЦЛЗТЗ

ЁЁЕуЖдЕубгГй

ЁЁЁЁаоЖЉАцIEEE 1588-2008в§ШыСЫаТЕФЛњжЦРДВтСПТЗОЖбгГйЃЌГЦЮЊЁАЕуЖдЕуЁБ(P2P)бгГйЁЃгыжЎЯрБШЃЌЩЯЮФЬжТлЕФжїДгЛњжЦдђЪЧЁАЖЫЖдЖЫЁБ(E2E)бгГйЁЃдкжЇГжIEEE 1588-2008ЕФЭјТчжаЃЌжїЪБжгЩшБИПЩвдгыДгЪБжгЩшБИжБНгЯрСЌЃЌЛђепИєМИИіжаМЬеОЃЈМЖЃЉЯрСЌЁЃE2EбгГйЪЕМЪЩЯЪЧжїЪБжгЩшБИЕНДгЪБжгЩшБИЕФЁАзмЁБбгГйЃЌАќРЈЦфМфЕФЫљгажаМЬеОдкФкЁЃЕЋЪЧЃЌP2PбгГйдђНіЯогкСНИіжБНгЯрСЌЕФЩшБИЁЃЭЈаХТЗОЖЕФзмбгГйЕШгкЫљгажаМЬеОЕФP2PбгГйжЎКЭЁЃДгШЗБЃТЗОЖЖдГЦадЕФНЧЖШПДЃЌP2PЛњжЦПЩЬсЙЉИќИпЕФОЋЖШЁЃ

ЁЁЁЁШчЩЯЮФЫљЪіЃЌIEEE 1588-2008аТдіСЫPdelayReqЁЂPdelayRespКЭPdelayRespFollowupШ§жжЯћЯЂРДВтСПP2PбгГйЁЃетаЉЯћЯЂЕФЙЄзїЗНЪНгыЩЯЮФЫљЪіЗНЪНЯрЫЦЃЌЯъЧщЧыПДВЮПМЮФЯз3ЁЃ

ЁЁЁЁгАЯьЭЌВНадФмЕФвђЫи

ЁЁЁЁОЋаФЩшМЦЕФIEEE 1588ЩшБИФмЙЛЪЕЯжИпЖШОЋШЗЕФЪБжгЭЌВНЃЌЕЋвВБиаыСЫНтжБНггАЯьЭЌВНадФмЕФжївЊвђЫиЃЌЦфжаАќРЈЃК

ЁЁЁЁ1. ТЗОЖбгГйЃКШчЩЯЮФЫљЪіЃЌIEEE 1588ЕФТЗОЖбгГйВтСПМйЩшЭЈаХТЗОЖбгГйЪЧЖдГЦЕФЃЌМДЧАЯђТЗОЖЕФДЋЪфбгГйгыКѓЯђДЋЪфбгГйЯрЭЌЁЃДЫЭтЃЌдкбгГйВтСПЦкМфЃЌбгГйВЛгІБфЛЏЁЃВтСПЦкМфбгГйБфЛЏЛсЕМжТВЛЖдГЦКЭбгГйЖЖЖЏЃЌетНЋжБНггАЯьЭЌВНОЋЖШЁЃЫфШЛЮоЗЈдкIEEE 1588ЩшБИЕФБпНчжЎЭтПижЦбгГйЖдГЦадКЭЖЖЖЏЃЌЕЋШчЙћВтСПЛљгкгВМўЪБМфДСЃЌдђПЩдкЩшБИФкИФЩЦТЗОЖЖдГЦадКЭЖЖЖЏЁЃгЩгкжаЖЯбгЪБЁЂЛЗОГЧаЛЛКЭЯпГЬЕїЖШЃЌШэМўЪБМфДСЛсЕМжТУїЯдЕФЖЖЖЏЃЌЖјгВМўЪБМфДСдђВЛДцдкетвЛЮЪЬтЁЃ

ЁЁЁЁ2. ЪБжгЕФЦЏвЦКЭЖЖЖЏЬиадЃКжїЪБжгЕФЦЕТЪКЭЯрЮЛДњБэИњзйПижЦЯЕЭГЕФЪфШыЃЌДгЪБжгдђЪЧПижЦЖдЯѓЁЃжїЪБжгЕФШЮКЮЪББфааЮЊЖМЛсШХЖЏИУПижЦЯЕЭГЃЌЕМжТЮШЬЌКЭЫВЬЌСНжжЮѓВюЁЃвђДЫЃЌЪБжгЕФЦЏвЦКЭЖЖЖЏдНЕЭЃЌдђЭЌВНОЋЖШдНИпЁЃ

ЁЁЁЁ3. ПижЦЗЈдђЃКДгЪБжгЕїећШчКЮаЃе§ДгЪБжгЩшБИЕФЪБМфЮѓВюШЁОігкПижЦЗНЗЈЁЃПижЦЗЈдђВЮЪ§АќРЈНЈСЂЪБМфЁЂЙ§ГхКЭЮШЬЌЮѓВюЃЌЖМНЋжБНггАЯьЪБжгЭЌВНадФмЁЃ

ЁЁЁЁ4. ЪБжгЗжБцТЪЃКШчЭМ1ЫљЪОЃЌБОЕиЪБМфЕФЗжБцТЪгЩЪБжгЦЕТЪОіЖЈЃЛзюаЁЪБМфдіСПЮЊЪБжгаХКХЕФвЛИіжмЦкЁЃIEEE 1588-2002жЇГж1 nsЕФЪБМфЗжБцТЪЃЌIEEE 1588-2008дђжЇГж2ЈC16 nsЕФЪБМфЗжБцТЪЁЃ216 (!) GHzЃЈЩѕжС1 GHzЃЉЕФЪБжгЪЧВЛЯжЪЕЕФЁЃБОЕиЪБжгЕФСПЛЏЛсгАЯьБОЕиЪБМфВтСПКЭПижЦЕФОЋЖШЁЃ

ЁЁЁЁ5. SyncЯћЯЂЕФЗЂЫЭжмЦкЃКДгЪБжгЕФИќаТЦЕТЪзюжеЛсгАЯьЭЌВНОЋЖШЁЃвђЮЊЪБМфЮѓВюЪЧДгЪБжгЦЕТЪЮѓВюЕФећЬхРлЛ§жЕЃЌЫљвдЗЂЫЭжмЦкдНГЄЃЌЯТвЛИіSyncЫљЙлВьЕНЕФЪБМфЮѓВювЛАуЛсдНДѓЁЃ

ЁЁЁЁ6. бгГйВтСПЕФЦЕТЪЃКвддЄЦкЯрСкВЩбљЕужЎМфбгГйУЛгаУїЯдБфЛЏЕФМфИєЪБМфЃЌЖЈЦкжДаабгГйВтСПЁЃШчЙћIEEE 1588ЭјТчЕФбгГйБфЛЏНЯДѓЃЌдђдіМгбгГйВтСПЦЕТЪПЩвдИФЩЦЪБжгЭЌВНадФмЁЃ

ЁЁЁЁФФИіЪЧжїЪБжгЃП

ЁЁЁЁдкПМТЧШчКЮОЋШЗШЗЖЈжїЪБжгЩшБИгыДгЪБжгЩшБИжЎМфЕФЪБМфВюжЎКѓЃЌЯТвЛИіЯрЙиЮЪЬтЪЧЃКдкГЩАйЩЯЧЇЬЈЛЅСЌЩшБИжаЃЌШчКЮШЗЖЈФФвЛЬЈЩшБИГфЕБжїЪБжгЁЃ

ЁЁЁЁEEE 1588ЖЈвхСЫвЛжжГЦЮЊЁАзюМбжїЪБжгЁБ(BMC)ЫуЗЈЕФЗНЗЈЃЌгУгкбЁдёжїЪБжгЩшБИЁЃетжжЗНЗЈвЊЧѓIEEE 1588ЭјТчЕФУПЬЈЩшБИОљЬсЙЉвЛИіЪ§ОнМЏЃЌУшЪіЦфБОЕиЪБжгЕФаджЪЁЂжЪСПЁЂЮШЖЈадЁЂЮЈвЛЪЖБ№ЗћКЭЪзбЁЩшжУЁЃЕБвЛЬЈЩшБИМгШыIEEE 1588ЭјТчЪБЃЌЫќЛсЙуВЅЦфЪБжгЕФЪ§ОнМЏЃЌВЂНгЪеЫљгаЦфЫќЩшБИЕФЪ§ОнМЏЁЃРћгУЫљгаВЮгыЩшБИЕФЪ§ОнМЏЃЌУПЬЈЩшБИОљдЫааЭЌвЛBMCЫуЗЈЃЌвдШЗЖЈжїЪБжгМАЦфздМКЕФЮДРДзДЬЌЃЈжїЪБжгЛђДгЪБжгЃЉЁЃгЩгкЫљгаЩшБИОљВЩгУЭЌбљЕФЪ§ОнЖРСЂжДааЭЌвЛЫуЗЈЃЌвђДЫНсТлНЋЛсЯрЭЌЃЌЩшБИжЎМфВЛашвЊНјааШЮКЮаЩЬЁЃгаЙиBMCЫуЗЈЕФИќЖрЯъЯИаХЯЂЃЌЧыПДВЮПМЮФЯз2КЭ3ЁЃ

ЁЁЁЁADSP-BF518ДІРэЦїжЇГжIEEE 1588

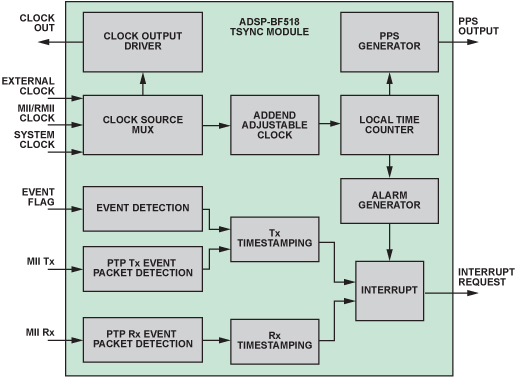

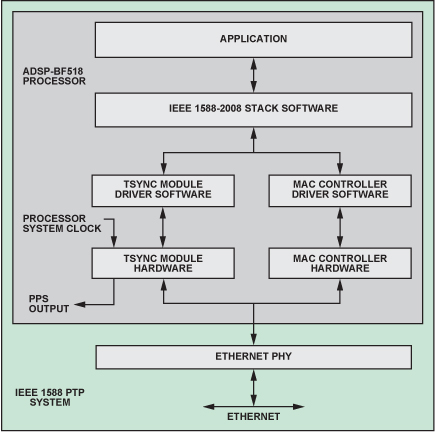

ЁЁЁЁADIЙЋЫОBlackfin DSPЯЕСазюНќаТдівЛПюВњЦЗЃКADSP-BF518ДІРэЦїЁЃЯёЧАПюВњЦЗADSP-BF537,4вЛбљЃЌИУДІРэЦїФкжУЁАвдЬЋЭјУНЬхЗУЮЪПижЦЦїЁБ(EMAC)ФЃПщЁЃЫќЛЙОпгаTSYNCФЃПщЃЌНјвЛВНРЉеЙСЫжЇГжIEEE 1588БъзМEMACЙІФмЕФФмСІЃЛЛЙЬсЙЉЦфЫќЖюЭтЬиадЃЌПЩжЇГжвдЬЋЭјЕФИїжжIEEE 1588гІгУЁЃЭМ5ЯдЪОСЫTSYNCФЃПщЕФПђЭМЁЃ ADSP-BF51x BlackfinДІРэЦїгВМўВЮПМЬсЙЉСЫИќЖраХЯЂЁЃ5

ЁЁЁЁ

ЁЁЁЁЭМ5. ADSP-BF518ДІРэЦїTSYNCФЃПщЕФПђЭМ

ЁЁ ЗжзщМьВт

ЁЁЁЁADSP-BF518ДІРэЦїПЩвдМьВтIEEE 1588ЕФЫљгаЪТМўЯћЯЂЃЌАќРЈЫЭШыКЭЫЭГіЕФЗжзщЃЌВЂЮЊЦфЬсЙЉгВМўЪБМфДСЁЃвђЮЊЪТМўЯћЯЂЪБМфДСЕФОЋЖШМАЦфЬсШЁЮЛжУЛсгАЯьТЗОЖбгГйЕФЖдГЦадКЭЮШЖЈадвЊЧѓЃЌЫљвдIEEE 1588ЯЕЭГЕФОЋЖШдкКмДѓГЬЖШЩЯШЁОігкетЖўепЁЃADSP-BF518ЕФTSYNCФЃПщГжајМрПиMACПижЦЦїгывдЬЋЭјЁАЮяРэНгПкЪеЗЂЦїЁБ(PHY)жЎМфЕФгВМўНгПкЃЌМДЁАУНЬхЖРСЂНгПкЁБ(MII)ЃЌВЂЧвжЛвЊМьВтЕНЪТМўЯћЯЂЃЌОЭЛсВњЩњгВМўЪБМфДСЃЌетвЛЙІФмПЩЬсИпADSP-BF518ЕФЭЌВНОЋЖШЁЃ

ЁЁЁЁЪТМўЯћЯЂМьВтЙІФмЪЧПЩБрГЬЕФЃЌЛљБОХфжУгаСНжжЃКжЇГжIEEE 1588-2002ЃЈФЌШЯзДЬЌЃЉЛђжЇГжIEEE 1588-2008ЁЃДЫЭтЃЌетжжПЩБрГЬФмСІЛЙжЇГжНЋРДАцБОЕФIEEE 1588ЃЌвдМАЦфЫќвЊЧѓЪБМфДСЕФвЛАуавщЃЌАќРЈХфжУЮЊИјНјГіДІРэЦїЕФУПИівдЬЋЭјЗжзщМгЩЯЪБМфДСЁЃ

ЁЁЁЁСщЛюЕФЪБжгдД

ЁЁЁЁБОЕиЪБжгЕФЪєадЖдгкIEEE 1588ЯЕЭГЕФадФмКмживЊЁЃЮЊСЫТњзуИїжжВЛЭЌгІгУЕФвЊЧѓЃЌADSP-BF518ДІРэЦїПЩЬсЙЉШ§жжБОЕиЪБжгдДбЁЯюЃКЯЕЭГЪБжгЁЂЭтВПЪБжгЛђвдЬЋЭјЪБжгЁЃШчЙћгІгУОпгаЬиЖЈЪБжгвЊЧѓЃЌдђПЩвдбЁдёЁАЭтВПЪБжгЁБЃЌВЂЬсЙЉЖЈжЦЪБжгдДЁЃШчЙћжїЪБжгЩшБИгыДгЪБжгЩшБИЁАБГППБГЁБСЌНгЃЌгЩгкЁАвдЬЋЭјЪБжгЁБРДздвдЬЋЭјЯпТЗЃЌЖјЧвСНЬЈЩшБИВЩгУЭЌвЛЪБжгЙЄзїЃЌвђДЫИУЪБжгбЁЯюПЩвдЬсЙЉСМКУЕФОЋЖШЁЃвЛАугІгУПЩвдбЁдёДІРэЦїЕФЁАЯЕЭГЪБжгЁБзїЮЊЪБжгдДЁЃ

ЁЁЁЁЫљбЁдДЪБжгвВгЩTSYNCФЃПщЧ§ЖЏЃЌЭЈЙ§ЬиЖЈв§НХClockoutзїЮЊДІРэЦїЪфГіЃЌЯЕЭГЕФЦфЫќВПЗжПЩРћгУИУЪфГіЬсЙЉБОЕиЪБМфаХЯЂЁЃ

ЁЁЁЁPPSЪфГі

ЁЁЁЁЁАУПУыТіГхЁБ(PPS)аХКХЪЧЪБМфаХЯЂЕФЮяРэБэЪОЁЃЫќУћвхЩЯЪЧвЛИі1-HzаХКХЃЌдкУПИі1УызЊЛЛЪБМфЗЂГівЛИіТіГхЁЃЫќПЩгУРДПижЦБОЕиЩшБИЃЌЛђепдкЗЂЩњЭјТчЙЪеЯЪБЬсЙЉИЈжњЪБМфЭЈЕРЁЃЫќвВПЩвдгУгкВтЪдЁЃСНЬЈЩшБИЕФPPSаХКХжЎМфЕФЯрЮЛВюЪЧЖўепЪБМфЦЋвЦЕФЮяРэСПЖШЁЃ

ЁЁЁЁADSP-BF518ДІРэЦїЬсЙЉСщЛюЕФPPSЪфГіЁЃЫќРћгУПЩБрГЬЁАПЊЪМЪБМфЁБ(PPS_ST)КЭжмЦк(PPS_P)ВњЩњвЛИідкЪБМф(PPS_ST + n ЁС PPS_P)ЗЂГіТіГхЕФаХКХЃЌЦфжаn = 1, 2, 3ЁЁЃЛљБОгУЗЈЪЧНЋPPS_PЩшжУЮЊ1УыЃЌВЂНЋPPS_STЩшжУЮЊгУУыЪ§БэЪОЕФНЋРДШЮвЛЪБПЬЃЌДгЖјВњЩњPPSаХКХЁЃВЮПМЛљБОгУЗЈЃЌПЩвдРћгУетжжPPSЪфГіЙІФмВњЩњОпгаПЩБрГЬЦЕТЪКЭПЊЪМЪБМфЕФжмЦкадаХКХЁЃ

ЁЁЁЁИЈжњПьее

ЁЁЁЁвЛаЉгІгУПЩФмашвЊАДееБъжОаХКХЧаЛЛжИЪОЃЌИјФГвЛЪТМўМгЩЯЪБМфДСЁЃADSP-BF518ЕФTSYNCФЃПщЭЈЙ§ИЈжњЁАПьееЁБЙІФмЃЌЪЙгУвЛИізЈгУв§НХРДНгЪеЭтВПБъжОЃЌвдБуЪЕЯжетжжЧыЧѓЁЃЧаЛЛБъжОНЋДЅЗЂИУФЃПщВЖзНЪБМфДСМФДцЦїжаЕФЕБЧАБОЕиЪБМфЃЌЙЉШэМўЗУЮЪЁЃ

ЁЁЁЁБЈОЏ

ЁЁЁЁШчЙћгІгУашдкЬиЖЈЪБМфжДаавЛЯюШЮЮёЃЌдђПЩвдгУTSYNCФЃПщЕФЁАБЈОЏЁБЙІФмЁЃетЯюЙІФмПЩвдЩшжУБОЕиОјЖдЪБМфЃЌЕНДяИУЪБМфЪБЃЌОЭЛсДЅЗЂДІРэЦїжаЖЯЁЃШЛКѓЃЌШэМўБуПЩРћгУжаЖЯжДааШЮЮёЁЃ

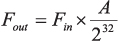

ПЩЕїЪБжг

ЁЁЁЁTSYNCФЃПщЕФПЩЕїЪБжгЪЧвЛжжЁАЛљгкМгЪ§ЁБЕФЪБжгЁЃШчЭМ6ЫљЪОЃЌЫќЛёЕУвЛИіЙЬЖЈЪфШыЪБжгаХКХЃЌВЂЪфГіИУЪфШыЕФЁАЕСШЁТіГхЁБАцБОаХКХЃКЖдгкУПИіЪфШыЪБжгЃЌЁАМгЪ§ЁБЕФжЕдіМгЕНРлМгЦїжаЃЌВЂЧвУПДЮРлМгЦївчГіЪБЃЌНјЮЛЮЛОЭЛсЧ§ЖЏЁАБОЕиЪБМфМЦЪ§ЦїЁБЃЌДгЖјВњЩњвдТіГхМЦЪ§жЕБэЪОЕФБОЕиЪБМфЁЃИќИФМгЪ§ПЩвдЕїећБОЕиЪБжгЕФЦЕТЪЃЌвђЮЊМгЪ§ОіЖЈРлМгЦївчГіЕФЦЕТЪЃЌДгЖјОіЖЈБОЕиЪБМфМЦЪ§ЦїЕндіЕФЦЕТЪЁЃШчЙћЪфШыЪБжгЕФЦЕТЪЮЊFinЃЌЧвМгЪ§ЕФжЕЮЊAЃЌдђБОЕиЪБжгЦЕТЪЮЊЃК

ЁЁЁЁ  (7) (7)

ЁЁЁЁ

ЁЁЁЁЭМ6. ЛљгкМгЪ§ЕФПЩЕїЪБжг

ЁЁЁЁВЩгУADSP-BF518ДІРэЦїЕФIEEE 1588ЪЕЪЉЗНАИ

ЁЁЁЁADSP-BF518ДІРэЦїЩЯЙЙНЈСЫвЛИіЭъећЕФIEEE 1588-2008МцШнЯЕЭГЃЌШчЭМ7ЫљЪОЁЃ

ЁЁЁЁЭМ7. ВЩгУADSP-BF518ЕФIEEE 1588ЪЕЪЉЗНАИ

ЁЁЁЁДІРэЦїЕФTSYNCФЃПщМьВтЫЭШыКЭЫЭГіЕФIEEE 1588ЯћЯЂЃЌВЂЭЈЙ§гВМўИјЪТМўЯћЯЂМгЩЯЪБМфДСЁЃгЩIXXAT (IXXAT Automation GmbH)ЬсЙЉЕФIEEE 1588авщеЛШэМўПЩЪЕЯжБъзМЫљвЊЧѓЕФЯћЯЂНЛЛЛавщЁЃЫќРћгУTSYNCЧ§ЖЏГЬађЖСШЁЁЂаДШыВЂЕїећTSYNCЪБжгЃЌВЂЪЙгУMACПижЦЦїЧ§ЖЏГЬађдквдЬЋЭјMACВуЃЈПЊЗХЯЕЭГЛЅСЌФЃаЭЕФЕкЖўВуЃЉЗЂЫЭКЭНгЪеЯћЯЂЁЃЫќЛЙПЩЪЕЯжP2PбгГйВтСПЕФПижЦЗЈдђКЭЙ§ТЫЁЃвдЬЋЭјPHYбЁдёОпгаЕЭЖЖЖЏбгГйЬиадЕФNational Semiconductor DP838486 ЁЃЮЊМђУїЦ№МћЃЌTSYNCФЃПщЪБжгдДбЁдёДІРэЦїЕФЯЕЭГЪБжг(80 MHz)ЁЃ

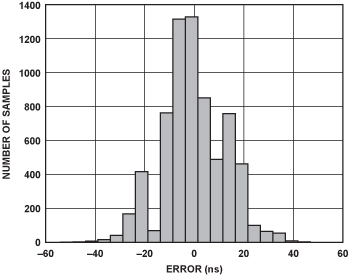

ЁЁЁЁЭМ8. ADSP-BF518ЩЯIEEE 1588ЯЕЭГЕФДгЪБжгЮѓВюжБЗНЭМ

ЁЁЁЁЭМ8ЪЧСНИіЭъШЋЯрЭЌЕФADSP-BF518 IEEE 1588ЯЕЭГжЎМфЕФВтСПЮѓВюжБЗНЭМЃЌгЩДЫПЩПДГіИУЦїМўЕФЪБжгЭЌВНадФмЁЃдкдМ1700УыЕФЪБМфФкЙВНјааСЫ6938ДЮВтСПЁЃзюжеЦНОљЮѓВюЮЊ0.015 nsЃЌБъзМВюЮЊ12.96 nsЁЃИУВтЪдЫљгУЕФSyncЯћЯЂМфИєЮЊ0.25УыЁЃ

ЁЁЁЁНсТл

ЁЁЁЁIEEE 1588БъзМЬсЙЉСЫвЛжжИпОЋЖШЁЂЕЭГЩБОЕФЗжВМЪНЪБжгЭЌВНЗНЗЈЁЃЫфШЛIEEE 1588ВЂЮДУїЮФвЊЧѓгВМўжЇГжЃЌЕЋгВМўИЈжњЯћЯЂМьВтКЭЪБМфДСЖдгкЪЕЯжМЋИпЭЌВНОЋЖШжСЙиживЊЁЃADSP-BF518ЮЊIEEE 1588-2002КЭIEEE 1588-2008ЬсЙЉгВМўжЇГжЃЌАќРЈИїжжгІгУЕФжЇГжЙІФмЁЃРћгУADSP-BF518ДІРэЦїКЭIXXAT IEEE 1588-2008авщШэМўЪЕЪЉIEEE 1588ММЪѕЃЌвбжЄУїПЩвдЪЕЯжИпОЋЖШЪБжгЭЌВНЁЃЁЁЁЁ |