数字波束形成技术充分利用阵列天线所获取的空间信息,通过信号处理技术使波束获得超分辨率和低副瓣的性能,实现了波束的扫描、目标的跟踪以及空间干扰信号的零陷,因而数字波束形成技术在雷达信号处理、通信信号处理以及电子对抗系统中得到了广泛的应用。数字波束形成是把阵列天线输出的信号进行AD采样数字化后送到数字波束形成器的处理单元,完成对各路信号的复加权处理,形成所需的波束信号。只要信号处理的速度足够快,就可以产生不同指向的波束。由于数字波束形成一般是通过DSP或FPGA用软件实现的,所以具有很高的灵活性和可扩展性。本文主要介绍了一个自适应波束形成器的原理及其实现方法,结合当今最先进的可编程芯片,包括数字信号处理器(DSP),现场可编程逻辑门阵列(FPGA)实现了数字波束形成,适用于如3坐标雷达系统等复杂阵列信号处理系统。其研制成果已应用在多部相控阵雷达中,缩小了我国在这个领域与其他国家之间的差距,具有重要的经济意义和军事意义。

1 数字波束形成系统的基本结构

采用数字方法对阵元接收信号加权处理形成天线波束,阵列天线阵元的方向图是全方向的,阵列的输出经过加权求和后,将阵列接收的方向增益聚集在一个方向上,相当于形成了一个波束,这就是数字波束形成的物理意义。数字波束形成器一般由两个主要部分组成,一部分是以数字信号处理器和自适应算法为核心的最优(次优)权值产生网络,另一部分是以动态自适应加权网络构成的自适应波束形成网络。波束形成算法是波束形成的核心和理论基础,他通过接收的信号和一些先验知识计算出加权因子,然后再对输入的信号在波束形成网络中进行加权处理完成波束形成。

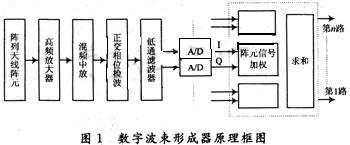

当进行多波束形成时,系统基本构成如图1所示。阵列天线每个阵元收到的信号经过混频、中放和正交相位检波,变为正交视频信号I和Q分量,再分别经由AD变换器转变为数字量I和Q,将数字信号送入波束形成运算器,分别与N组权值进行复数乘法运算,即得到所需的N个波束通道的信号。数字波束形成运算器由FPGA通过编程实现,主要进行权值的存储和把各路波束所需的权值信息存储于FPGA内部的存储模块中,通过进行乘加运算,来实现多波束的产生。

本文选用Altera公司的STRATIX器件,及其仿真软件QuartusⅡ4.1,运用VHDL语言与Altera的megafun-citions模块化函数库相结合编程设计来实现数字多波束形成器。文中举例所用的天线阵为N阵元等距线阵,在数字波束形成部分要实现十路数字波束形成。

2 基于FPGA和ADSP器件的数字波束形成器的实现

2.1硬件组成

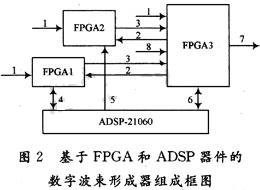

数字波束形成器由3片FPGA和1片ADSP-21060器件来实现,其中第一片和第二片FPGA完成输入接收通道的校正以及复数乘法累加运算并最终形成十个波束;第三片FPGA完成整个系统的的时序和模式控制并将前两片FPGA运算的结果合成后输出,需要时副瓣对消的运算也在这一片完成。ADSP-21060器件主要完成接收通道校正系数和波束形成系数的实时计算,需要时进行副瓣对消系数的计算和发射通道校正运算。系统组成框图如图2所示。

其中总线上的标号解释如下:

1:输入的多通道A/D中频采样后的数字信号;

2:第三片FPGA传输控制信号给前两片FPGA;

3:前两片FPGA乘法累加运算结果输出到第三片FPGA;

4,5,6:ADSP-21060与FPGA的数据总线;

7:数字波束形成器的最终输出数据;

8:外部输入的模式控制信号。

为了让硬件平台具有很强的通用性,对于FPGA器件,选用了Altera公司含有大容量片内RAM和硬件乘法器的Stratix系列的EPlS60芯片,该芯片有18个硬件乘法器模块,内部存储空间达到5 215 kb,逻辑单元数达到了57 120 les,完全能满足此波束形成器的实现,并能利用冗余空间放置其他运算单元和控制模块,基本实现了系统的集成化模块化设计。且此器件的运算频率完全满足需要,片内大量的剩余资源空间可以提供给后续部分的使用。

最终3片FPGA芯片的资源占用情况分别为:对于FPGAl芯片,编译后的资源为占用18个硬件乘法单元,占用1 680 kb/s片内存储空间,占用逻辑资源16 791 les;对于FPGA2芯片,编译后的资源为占用18个硬件乘法单元,占用1 680 kb片内存储空间,占用逻辑资源15 608 les;对于FPGA3芯片,编译后的资源占用为占用0个硬件乘法单元,占用103 kb片内存储空间,占用逻辑资源7 599 les。由以上具体数据可见,对于FPGA1和FPGA2芯片,因为需要做大量的乘法累加运算,芯片的硬件乘法单元已全部占用,但片内存储空间只占用了32%,逻辑单元最多也只占用了不到30%。 |