| 1 引言

疲劳驾驶是造成交通事故的主要原因之一。据统计,驾驶疲劳造成的交通事故无论是绝对数字还是所占比例都是最高的。如何有效检测驾驶员的疲劳状态,并在其出现睡意时给予警告或提醒其停车休息已成为研究热点。应用驾驶员疲劳检测系统主动预防交通事故,可以在一定程度上减少交通事故的发生,减少交通事故带来的危害,使驾驶员驾驶和公众出行更安全。目前国内外驾驶员疲劳检测的方法可归纳为3种:①监测司机个体行为特征,例如,眼睑的活动,点头的动作,闭眼,握力等;②监测司机的生理信号,如心电图、脑电图、肌肉活动情况等;③监测车辆参数,速度、加速度等。PERCLOS是一种通过检测驾驶员眼睛的闭合程度信息的方法反映驾驶员的疲劳,它能准确地反映疲劳状态。因此,这里提出一种基于ADSP-BF533控制器和PERCLOS方法的非接触式、实时性较强的驾驶员疲劳检测系统设计方案,此系统可以准确检测驾驶员的疲劳状况,并给出警告。

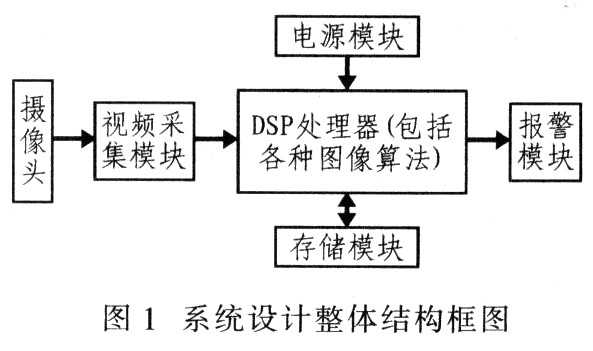

2 系统概述

该系统采用ADI公司Blackfin系列的高性能体系结构的定点DSP处理器BF533为核心处理器,它具有2个MAC信号处理引擎,采用正交类 RISC微处理器指令集,特有的专用视频指令使其具有显著的视频处理性能。前端采用CN00-303ROFD0摄像头实时采集驾驶员面部图像信息,然后通过PPI接口以DMA方式将数据传送到SDRAM中,每传送完一帧图像,BF533处理器通过运行的疲劳检测程序分析输入数据和视频流,检测驾驶员的疲劳状况,并对视频MPEG-4编码,保存到IDE硬盘。当检测到驾驶员疲劳时可通过ISDl700发出语音告警。系统设计整体结构框图如图1所示:

3 系统硬件设计

系统硬件设计主要由视频采集模块、存储系统、语音报警模块和电源模块等4部分组成。

3.1 视频采集模块

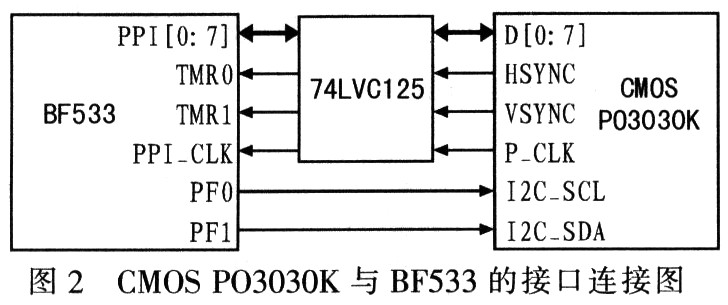

视频采集是该系统设计非常重要的部分。采集的图像分辨率大小将直接影响DSP的处理效果。CMOS图像传感器选用PO3030K,该器件像素阵列为 640×480,具有缺陷纠正、边缘增强、色彩纠正、自动白平衡、自动曝光控制、反射光补偿等功能,其数据输出格式有:YCbCr4:2:2、 YUV4:2:2、5:6:5RGB、5:5:5RGB等多种模式,可通过I2C总线控制。CMOS图像传感器PO3030K与BF533的接口连接图如图2所示。

CMOS图像传感器的12C_SCL、12C_SDA引脚分别与BF533的PF0、PF1相连,其像素输出端口D0~D7与BF533的PPI0~PPI7相连,PO3030K的像素时钟作为PPI的驱动时钟。

3.2 存储器系统

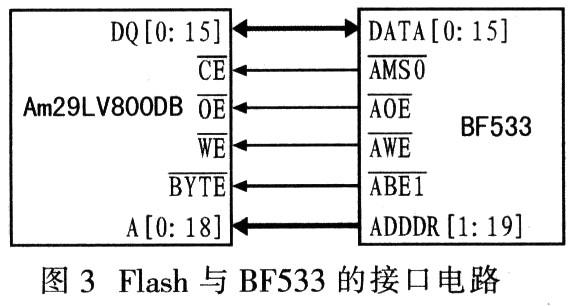

存储器系统包括程序存储器和数据存储器,程序存储器主要用于存储系统程序,数据存储器用于图像缓存和视频存储。程序存储器选用能电擦写、掉电保护的 Flash存储器Am29LV800DB,该器件为8 Mbit。数据宽度可配置成8位或16位。Am29LV800DB与BF533的接口连接如图3所示。

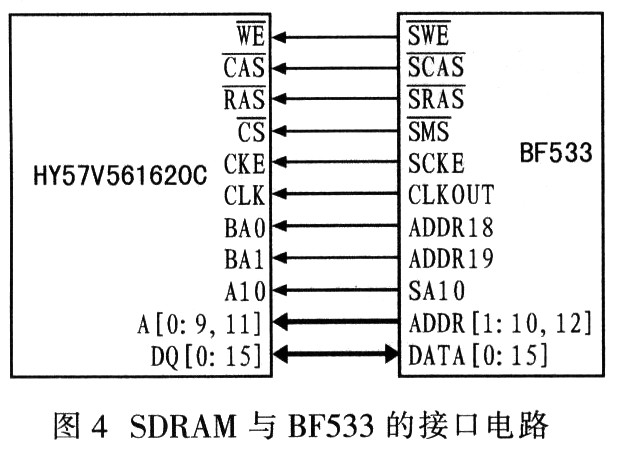

在处理图像中,由于图像数据量很大,BF533内存有限,所以系统外部扩展SDRAM做为数据缓冲区。SDRAM选用Hynix公司的 HY57V561620C,该器件是一款4 Bankx4 Mxl6Bit的同步高速动态存储器,完全满足数据缓冲的需要。HY57V561620C与BF533的接口连接如图4所示。

视频数据的存储采用大容量的ATA_IDE硬盘存储。ATA_IDE接口的硬盘为计算机最常用的存储设备,其总线接口方式与控制时序满足BF533的 EBIU接口的总线控制时序,可通过该接口直接与硬盘IDE接口连接。连接接口框图如图5所示,CPLD的作用是为IDE硬盘分配总线地址,IDE硬盘有两根地址线IDE_CS1和IDE_CS2。IDE_CS1选通命令块寄存器,命令块寄存器包含对硬盘读写控制的寄存器,通过配置这些寄存器对硬盘读写操作;IDE_CS2选通控制块寄存器,包含设备控制、状态读取等寄存器。由于硬盘的逻辑电平为5 V,BF533的逻辑电平为3.3 V为了使其相匹配,采用总线驱动器74LVC245为电平转换。74LVC245为双向8位总线驱动器,两片用于数据总线驱动,一片用于控制信号线的电平匹配。74LVC245传输数据方向的控制引脚DIR,其逻辑时序与BF533的读控制时序相同,将其连接在BF533的AOE引脚,以控制数据的传输方向。IDE在硬件连接上有两种工作模式:DMA传输模式和PIO传输模式。由于BF533的DMA控制器只是从接口到内存的控制,无法对外部器件做DMA 控制。如需实现硬盘的DMA传输模式,必须选用专用的DMA控制。为了简化硬件设计,选用PIO16位模式作为硬盘的控制模式。

来源EDN |