在做DSP开发的时候,一般都会用到SDRAM,下面总结一下ADI公司的SHARC系列的DSP和SDRAM的接口连接。

SDRAM工作电压为3.3V。硅版0.2或更高的ADSP-21369处理器的SDRAM控制器可以运行在166MHz.硅版0.0和0.1的SDRAM控制器仅能运行在133MHz.

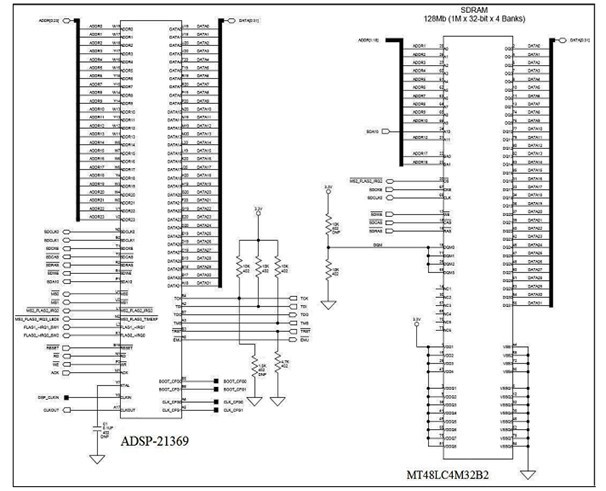

所选SDRAM的型号为MT48LC4M32B2,因为是32位SDRAM,因此要从ADDR1开始连接地址A0,并且A10要和SDA10相连。如果是16位的SDRAM则要从ADDR0开始连接地址A0.

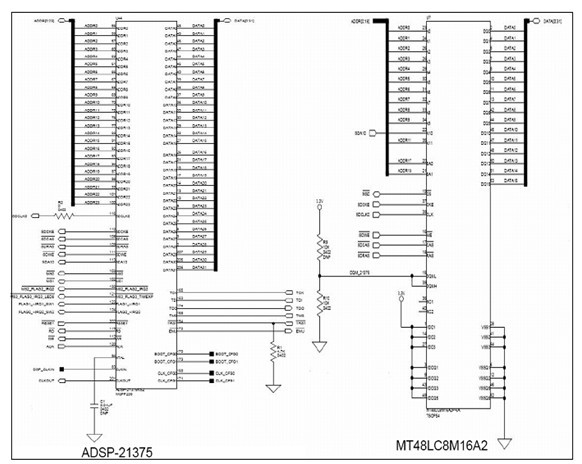

如图所示,Figure 1是和32-bit SDRAM 的硬件连接,用的是ADSP-21369评估板套件,Figure2是和16-bit SDRAM 的硬件连接, 用的ADSP-21375评估板套件。

图一

图二

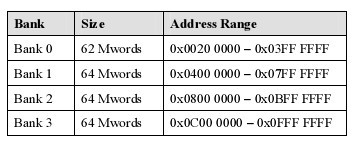

SDRAM能被分配到处理器四个地址块得任意一块,每一个地址块有片选MSx,用来驱动存储器的芯片选择信号CS.

下表是外部存储器SDRAM地址分配

一、要设置SDRAM控制器要按照下面的步骤:

(1)配置内核时钟与SDRAM的时钟比

SDRAM时钟(SDCLK)由处理器内核时钟(CCLK)产生。支持5个固定的比例:1:2.0、1:2.5、1:3.0、1:3.5和1:4.0.要得到期望的SDCLK,需针对采用的CCLK频率设置PLL.通过设置PMCTL寄存器来实现,同时要设置DIVEN位。

(2)配置处理器的PLL

在设置PMCTL寄存器的DIVEN位和将PLL设置为旁路模式之间有一个内核周期的延时。对PMCTL寄存器进行写操作来设置或清除旁路模式时,要清除DIVEN位,这就保证了PLL的配置正确。

(3)将SDRAM映射到外部存储器组中的一个

通过对外部端口控制(EPCTL)寄存器设置合适的BxSD位将SDRAM映射到4个外部存储器块中的一个

(4)配置SDC

第一步是用正确的刷新数值(RDIV)配置SDRRC寄存器并设置SDRAM读优化。第二步是将各个控制参数写入SDRAM控制寄存器(SDCTL).

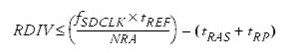

用正确的SDRAM刷新值对SDRRC寄存器的DIV域编程。由下式计算RDIV计数值得出该值。

式中:fSDCLK是SDCLK频率(SDRAM时钟频率)

tREF是SDRAM刷新周期

NRA 是SDRAM中行地址个数(刷新周期对整个SDRAM进行刷新)

tRAS是以时钟周期数为单位的激活到预充电时间(SDRAM存储控制【SDCTL】寄存器的SDTRAS位);

tRP是以时钟周期数为单位的RAS到预充电时间(在SDRAM存储控制【SDCTL】寄存器中)。

二、通用PCB设计指南:

(1)地址线和数据线越短越好

(2)可以不对SDCLK、DATA和ADDR进行端接。使用信号完整性(SI)工具来确定需要端接的信号。过多的端接会使信号升降缓慢,增加延时。

(3)处理器的I/O驱动可支持最高30pF的I/O负载。

(4)对每个存储器器件都要充分的去耦合。

(5)AVDD电源要使用处理器数据手册中指定的滤波电路设计。 |