转载--happysaisai的博客

今天继续上次博客介绍一下基于ADSP-21369实验教学系统的21369处理器设计。

(3)电源供电

本系统的DSP供电电源分为三种,内核电源(VDDINT)、I/O电源(VDDEXT)和模拟电源(AVDD/AVSS),它们由独立的电源供电连接。ADSP-21369芯片208引脚的封装共有四种,我们选择的是ADSP-21369KSWZ-2A,工作在333 MHz,内核和模拟电源为1.2 V,I/O电源供给满足3.3V要求,所有电源引脚必须连接到同一个供电电源上。模拟电源引脚(AVDD)是给处理器的内部时钟产生器PLL供电。要产生稳定的时钟,PCB设计时要为AVDD引脚加外部滤波电路,且滤波元件应尽可能靠近AVDD/AVSS 引脚。该电路设计如图1。为了降低噪声耦合,PCB上VDDINT 和GND应使用并行的电源和地线层对。AVDD和GND引脚的旁路电容要用较宽的连接线。

注意图1中指定的AVDD和AVSS引脚是处理器的输入,而不是板上的模拟地平面。芯片上应直接将AVSS引脚和数字地(GND)直接连接。

图1 模拟电源滤波电路

Figure 1 Analog power (AVDD) filter circuit

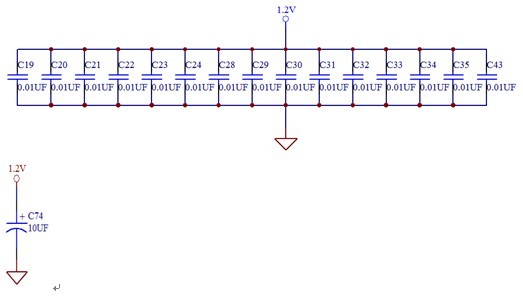

(4)旁路电容

内部电源在较高的工作频率下需要合适的旁路电容,旁路电容可以把输入信号中的高频噪声作为滤除对象,把前级携带的高频杂波滤除。电容器和路径中的寄生电感降低了系统在高频时的性能。处理器要工作在100MHz以上有两个要求。第一,电容要小、导线要短,这样就可以减少电感。型号为0402的贴片电容比体积大的电容效果好。第二,电容值越低,LC电路对频率的忍耐力越强。0.1μF的电容在500MHz以下工作的很好,但是0.1、0.01、0.001μF甚至100pF的电容混合后可使VDDINT的频率范围提高到500MHz。考虑到ADSP-21369芯片共有31个VDDINT引脚,我们设计了31个0.01μF的旁路电容,图2(左)表示出部分旁路电容。在低频信号地传递与放大过程中,为防止前后两级电路地静态工作点相互影响,常采用电容耦合,一般总采用容量较大的电解电容,如图2(右)所示。

图2 旁路电容及耦合电容

Figure 2 Bypass capacitors and coupling capacitor