转载--happysaisai的博客

今天来介绍一下基于ADSP-21369的实验教学系统的DSP处理器设计,DSP处理器设计是本套实验教学系统的核心,本课题选定的ADSP-21369处理能力强,时钟频率较高,外设接口丰富,能够很好的满足实验教学系统的需要,其硬件电路主要从以下几方面进行设计。

(1)系统时钟

系统时钟是任何系统能够正常运行的关键,系统时钟包括内核时钟和外围时钟,其中内核时钟是CPU的工作时钟,外围时钟是外围器件的工作时钟。处理器的内核时钟CCLK为同步内部存储器、处理器内核以及串行端口提供时钟信号。在复位的过程中,可以通过CLKCFG1-0管脚设置处理器内核时钟频率与外部时钟频率(CLKIN)的比值,参见表1。

表1 内核时钟和CLKIN的比值

Table 1 The ratio between the core clock and CLKIN

|

CLK_CFG1-0 |

内核时钟与CLKIN比 |

|

00 01 10 11 |

6:1 32:1 16:1 保留 |

处理器内部时钟转换速率比系统输入时钟(CLKIN)转换率更高。为了产生内核时钟,处理器使用了内部锁相环路(PLL),基于PLL可以将系统时钟信号与处理器内部时钟之间的相位差减到最小。需要注意的是各种时钟周期的定义是CLKIN的函数,适当的比率控制如表2和表3所示。

表2 ADSP-21369时钟生成操作

Table 2 the clock generation operation of ADSP-21369

|

时序要求 |

描述 |

计算 |

|

CLKIN CCLK |

输入时钟 内核时钟 |

1/tCK 1/tCCLK |

表2中,CCLK定义为:fCCLK= (2 x PLLM x fINPUT) / (2 x PLLN) 其中,fCCLK= CCLK频率,PLLM = 编程的乘数,PLLN =编程的除数。

表3时钟周期

Table 3 Clock periods

|

时序要求 |

描述 |

|

tCK tCCLK tPCLK tSCLK tSDCLK tSPICLK |

CLKIN时钟周期 (处理器)内核时钟周期 (外设)时钟周期=2* tCCLK 串行端口时钟周期= tCCLK*SR SDRAM时钟周期= tCCLK*SDR SPI时钟周期= tCCLK*SPIR |

表3中,SR为串行端口与内核时钟的比(由DIVx寄存器中的SPORT CLKDIV位决定),SPIR为SPI与内核时钟的比(由SPIBAUD寄存器设定来决定),SPICLK为SPI时钟,SDR为SDRAM与内核时钟的比(由PMCTL寄存去的20-18位决定其值)。

外部时钟频率(CLKIN)由外部时钟电路供给,外部时钟电路可以是晶体电路、晶振电路、可编程时钟芯片电路,我们将三种电路做一下对比:

1)晶体电路最为简单,只需晶体和2个电容,但驱动能力差,不能提供多个器件使用,频率范围小(20KHz-60MHz),使用时须注意配置正确的负载电容,以使输出的时钟频率精确、稳定。

2)晶振电路频率范围宽(1MHz-400MHz),驱动能力强,可为多个器件使用。但由于晶振频率不能改变,多个独立的时钟需要多个晶振。另外在使用晶振时,要注意时钟信号电平,一般晶振输出信号电平为5V或3.3V。

3)可编程时钟芯片电路由可编程时钟芯片、晶体和两个外部电容构成。有多个时钟输出,可产生特殊频率值,适用于多个时钟源的系统,驱动能力强,频宽最高可达200MHz,输出信号电平一般为5V或3.3V。

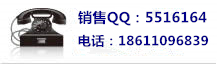

在本实验教学系统的设计中,需要多个时钟输入,而且对时钟质量要求很高,所以从时钟质量和成本两方面折中考虑,也为了将来系统稳定运行后可以方便的提高频率,本系统选取晶振电路的方式来设计时钟电路。程序可以设定通过给CLKIN和XTAL连接必要的元件,使处理器用其内部时钟产生器。图2是DSP芯片和晶振元件的连接图。

图1 DSP芯片和晶振元件的连接

Figure 1The connection between DSP chip and crystal oscillator

(2)程序加载

在系统上电后,程序是在DSP的RAM中执行的,但是RAM中的数据掉电后就会丢失,为了实现脱机工作,可以使用程序加载,处理器内部存储器可以通过外部接口从8位EPROM加载、SPI主机或从机加载、或者处理器从内部加载,加载方式由加载配置引脚确定(BOOT_CFG1–0) (参见表4)。通过SPI控制的加载源,既可以作为主机,也可以作为从机,或立即从ROM中开始执行。

表4 加载模式选择

Figure 4 Boot mode selections

|

BOOT_CFG1-0 |

加载模式 |

|

00 01 10 11 |

SPI从设备加载 SPI主设备加载 EPROM/FLASH加载 保留 |

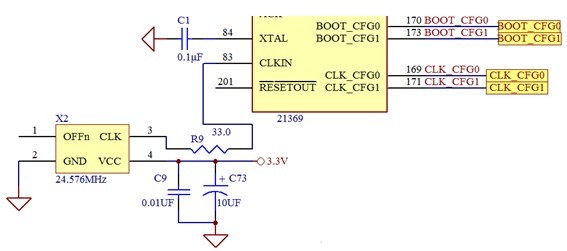

处理器内部时钟频率与外部时钟频率的比值(CLKIN)还有系统上电时的加载方式的选择是通过开关SW1配置的,电路图如图3所示。

图2 加载模式和时钟比率选择开关

Figure 2 Bootload mode and clock ratio selection switch